隨著摩爾定律逐漸放緩,晶體管尺寸微縮帶來的效能提升有限,半導體產業轉而依靠系統層級的封裝微縮來持續推動性能成長。封裝尺寸的縮小與鍵結技術,從早期的C4焊料發展到焊料/銅柱,再到現在的銅混合鍵合(Cu Hybrid Bonding),有效提升互連密度與電性表現。

即使2030年後背端製程(BEOL)微縮趨近極限,封裝微縮仍會持續。高密度的2.5D與3D混合鍵合技術成為彌補互連瓶頸的關鍵利器,先進封裝正加速向晶圓級與矽基製程平台發展,成為未來半導體產業重要的成長動力。

半導體設計與製造評估指標

| 技術類型 | RDL 間距 (pitch) | FC 凸點間距 | 封裝尺寸 | 封裝高度 | 成本 | 已量產技術範例 |

|---|---|---|---|---|---|---|

| 2.5D/3D TSI | ≤2μm(銅BEOL) | ≥20μm | >50×50 mm | — | 較高 | CoWoS-S、Foveros |

| 矽橋 (Si Bridge) | ≤2μm(銅BEOL) | ≥2μm | >50×50 mm | — | 低於TSI | EMIB、InFO-L |

| FOWLP | ≥4μm | ≥40μm(晶片-RDL) | — | 約200μm | 低 | eWLB、InFO |

| FCBGA | ≥20μm | ≥50μm | — | — | 低 | 一般量產 |

2.5D/3D TSI 技術因其高密度互連與大尺寸支援,擁有最大的擴展優勢;而矽橋技術則在互連密度與成本控制之間實現良好平衡,成為市場上的重要選擇。

TSI:Through Silicon Interposer,矽穿孔中介層

EMIB:Embedded Multi-Die Interconnect Bridge,嵌入式多晶片互連橋

InFO:Integrated Fan-Out,整合型扇出封裝

由於熔融焊料在鍵合過程中可控性有限,傳統C4凸塊的焊料接點難以縮小至20微米(μm)間距以下。為了突破互連密度的瓶頸,業界逐步轉向銅對銅直接鍵合及無凸塊混合鍵合技術,實現更細微、更可靠的互連結構。

Chiplet簡介

傳統的半導體封裝上的所有元件皆是單晶片設計與製造,Chiplet的概念則是先將CPU或GPU、SRAM、I/O等元件分別進行設計與製造,再整合成一個半導體。Chiplet可提升製品良率。半導體晶片面積越小 (晶片內出現缺陷的可能性越低)良率就越高。由於Chiplet是將多種不同製程(技術世代)的晶片相互組合而成,因此每個晶片都比與單晶片製品的面積更小。

Chiplet一般會被歸類於後端製程(Back end),但因需要高密度的佈線,也會使用到許多晶圓級製造技術等的前端製程(Front end)技術。需要被稱為「中段製程」(Mid-end of line, MEOL)的技術來銜接前段與後段製程之間。

Chiplet通訊規格有UCIe或BoW等。UCIe是PCIe的Chiplet 版本,因高延遲和需要訊號控制引腳等理由,間接成本較高 。BoW則是將Network on Chip擴張到晶片間介面,減少多餘的protocol處理、延遲較短,也獲得了一些實際成果,只是在標準化方面仍然不敵UCIe。

UCIe:Universal Chiplet Interconnect Express,通用晶片小塊互連標準

BoW:Bunch of Wires,大量線路/線束架構

設計與製程協同最佳化的關鍵技術

DTCO(Design Technology Co Optimization),自22nm/16nm節點開始導入的「 設計與製造協調最佳化」方法。特別是在FinFET,從設計規則和製程條件雙方面達到最佳化,以同時滿足消耗功率和性能和矽面積(PPA)的需求。

STCO(System Technology Co Optimization),自7nm節點起,因元件結構複雜化及Chiplet化,DTCO不足以對應,導入全新的「系統與製造協調最佳化」方法。除DTCO以外,將STCO應用於大規模的電路區塊或子系統,以實現消耗功率、性能、矽面積和成本(PPAC)的整體最佳化。

PPA:Power, Performance, Area,功耗、性能、面積

PPAC:Power, Performance, Area, Cost,功耗、性能、面積、成本

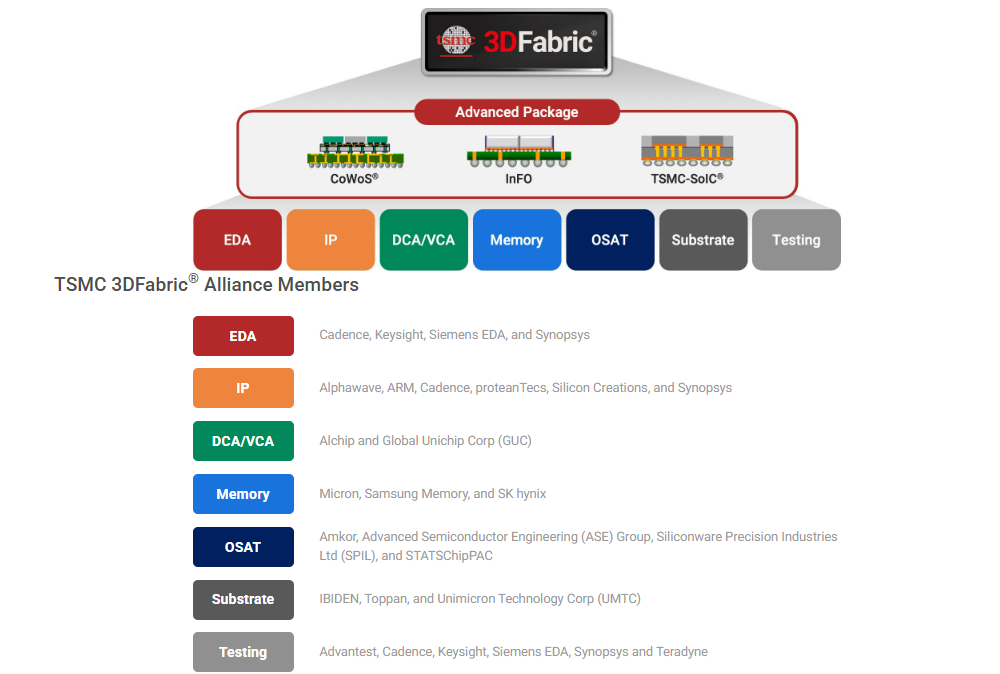

台積電(TSMC)3DFabric 的生態系統